| Xilinx FIFO Generator axi | 您所在的位置:网站首页 › stream generator › Xilinx FIFO Generator axi |

Xilinx FIFO Generator axi

|

FIFO Generator IP对应的手册为:pg057 FIFO Generator v13.2。 平台:vivado2017.4 芯片:kintex-7 xc7k325tffg900-2 准备学习AXI总线。上一篇学习了AXI BRAM。这一篇学习AXI FIFO。 目录 IP介绍 测试代码 仿真波形 IP介绍新建FIFO Generator使用AXI Stream接口。选择独立时钟。AXI_Stream允许配置端口有TDATA,TID,TDEST,TUSER。对于TKEEP和TSTRB信号将由TDATA决定。其他配置默认。 翻阅手册查看AXI Interface FIFOS介绍。

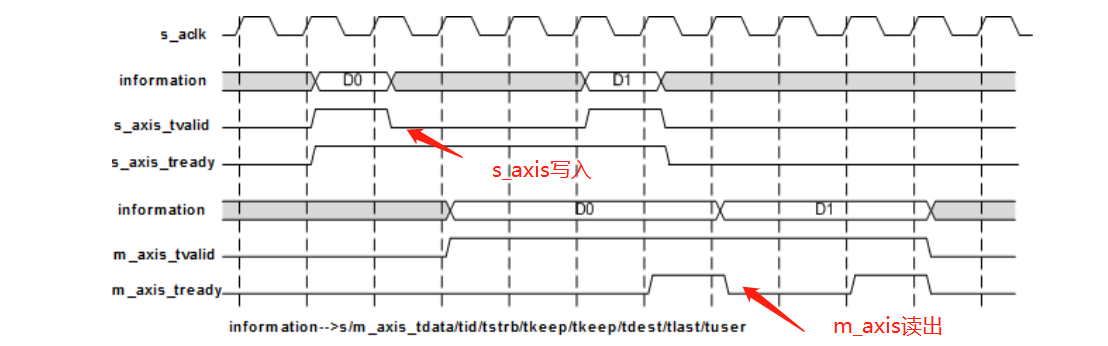

AXI接口来自于原生接口FIFO,从上图中可以看出。FIFO的复位,读写时钟分别和AXI的复位和时钟同步。 其中AXI特色的握手信号。 对于写通道,主向FIFO内写,主的valid信号和FIFO的写使能关联,FIFO的满信号对主提供ready信号。从图中可以看出,FIFO不满的情况下,ready信号将置一。主的写数据通道侧的信号将作为FIFO的写数据。 对于读通道,从机从FIFO内读出,从机向FIFO提供的ready信号作为FIFO的读使能。FIFO则将自己empty信号作为从机valid,即FIFO内有数据从机既可以读取。从机读数据通道侧信号将作为FIFO的读数据。 AXI4-StreamFIFO的写入和读操作示例时序图。

从图中可以看出来,写入数据是在s_axis_tvalid和s_axis_tready信号同时有效时才将数据写入到FIFO。同理读出数据是在m_axis_tvalid和m_axis_tready同时有效时读出。但是读数据时,FIFO会将第一个数据同m_axis_tvalid拉高的同时将数据放在m_axis_tdata上。等待m_axis_tvalid和m_axis_tready同时有效时读出。 下面我们来做仿真。 测试代码首先,例化FIFO,将接口引出。 // *********************************************************************************/ // Project Name : // Author : i_huyi // Email : [email protected] // Creat Time : 2021/8/7 14:53:43 // File Name : .v // Module Name : // Called By : // Abstract : // // CopyRight(c) 2020, xxx xxx xxx Co., Ltd.. // All Rights Reserved // // *********************************************************************************/ // Modification History: // 1. initial // *********************************************************************************/ // ************************* // MODULE DEFINITION // ************************* `timescale 1 ns / 1 ps module axis_fifo_control#( parameter U_DLY = 1 ) ( input wire wr_clk , input wire rd_clk , input wire rst , output wire[10:0] axis_wr_data_count , output wire[10:0] axis_rd_data_count , //全局信号 //全局信号 output wire wr_rst_busy , output wire rd_rst_busy , //axis_wr_interface input wire s_axis_tvalid ,//输入数据有效(相当于写使能) output wire s_axis_tready ,//axis_fifo准备好接收数据 input wire[31:0] s_axis_tdata ,//axis_fifo接收的数据 input wire s_axis_tlast ,//传输的最后一个数据 input wire[3:0] s_axis_tuser ,//自定义传输辅助信息内容 //axis_rd_interface output wire m_axis_tvalid ,//fifo数据有效(FIFO内有数据) input wire m_axis_tready ,//读数据准备就绪(相当于读使能) output wire[31:0] m_axis_tdata ,//读出的数据 output wire m_axis_tlast , output wire[3:0] m_axis_tuser ); //-------------------------------------- // localparam //-------------------------------------- //-------------------------------------- // register //-------------------------------------- //-------------------------------------- // wire //-------------------------------------- wire s_aresetn ; //-------------------------------------- // assign //-------------------------------------- assign s_aresetn = ~rst ; //assign m_axis_tready = 1'b0; //------------------------------------------------------------ //------------------------------------------------------------ //----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG fifo_generator_0 u_fifo_generator_0 ( .wr_rst_busy (wr_rst_busy ),// output .rd_rst_busy (rd_rst_busy ),// output .m_aclk (wr_clk ),// input .s_aclk (rd_clk ),// input .s_aresetn (s_aresetn ),// input .s_axis_tvalid (s_axis_tvalid ),// input .s_axis_tready (s_axis_tready ),// output .s_axis_tdata (s_axis_tdata ),// input [31:0] .s_axis_tlast (s_axis_tlast ),// input .s_axis_tuser (s_axis_tuser ),// input [3:0] .m_axis_tvalid (m_axis_tvalid ),// output .m_axis_tready (m_axis_tready ),// input .m_axis_tdata (m_axis_tdata ),// output [31:0] .m_axis_tlast (m_axis_tlast ),// output .m_axis_tuser (m_axis_tuser ),// output [3:0] .axis_wr_data_count (axis_wr_data_count ),// output [10:0] .axis_rd_data_count (axis_rd_data_count ) // output [10:0] ); //------------------------------------------------------------ //------------------------------------------------------------ //------------------------------------------------------------ //------------------------------------------------------------ endmodule在顶层上分别例化axis_FIFO和axi_bram。为了实现两者之间相互通信。 这里我们先做axis_FIFO的仿真。思路为,首先发送发先向axis_FIFO发送100个数据。在FIFO里面的数据个数达到100个,在将里面的数据一次性读出。并结束操作。注意在AXI总线中,作为发送方时,发送方不能等待先等待接收方给出READY信号在给出VALID信号。而是VALID信号是发送方一个完全主动的操作,表示我已经准备好发送数据,接收方判断自己是否能够接收,在拉高READY信号。下面看具体的代码操作: //------------------------------------------------------------ //------------------------------------------------------------ //自测试,fifo产生数据,先写后读 //FIFO写,先等待tready信号有效,表示FIFO里面可以写入数据 always@(posedge lb_clk or posedge lb_rst) begin if(lb_rst == 1'b1) begin s_axis_tvalid |

【本文地址】